世界はAIに熱狂しており、ソフトウェア企業はテキスト、画像、動画を生成する膨大な需要を賄うために、原子力発電への投資にまで踏み込んでいる。だが、もしその必要がないとしたらどうだろう。効率を90%高めることで、より低コスト、はるかに少ないエネルギー消費で、より多くのことを実現できる──AIの恩恵を余すところなく享受できるとしたらどうだろう。

これが、マイクロソフトが出資するチップ新興企業d-Matrixの売り文句である。核心となるアイデアは、はるかに高速で安価、かつ効率的な推論を実現するチップを作ることだ。推論とは、AI企業がユーザーの問いかけに対して回答を生成する処理のことである。d-Matrixの主張が正しければ、AIの未来を左右するのは「誰が最大のモデルを学習させるか」ではなく、「誰が最も速く、最も安く答えを返せるか」になるかもしれない。

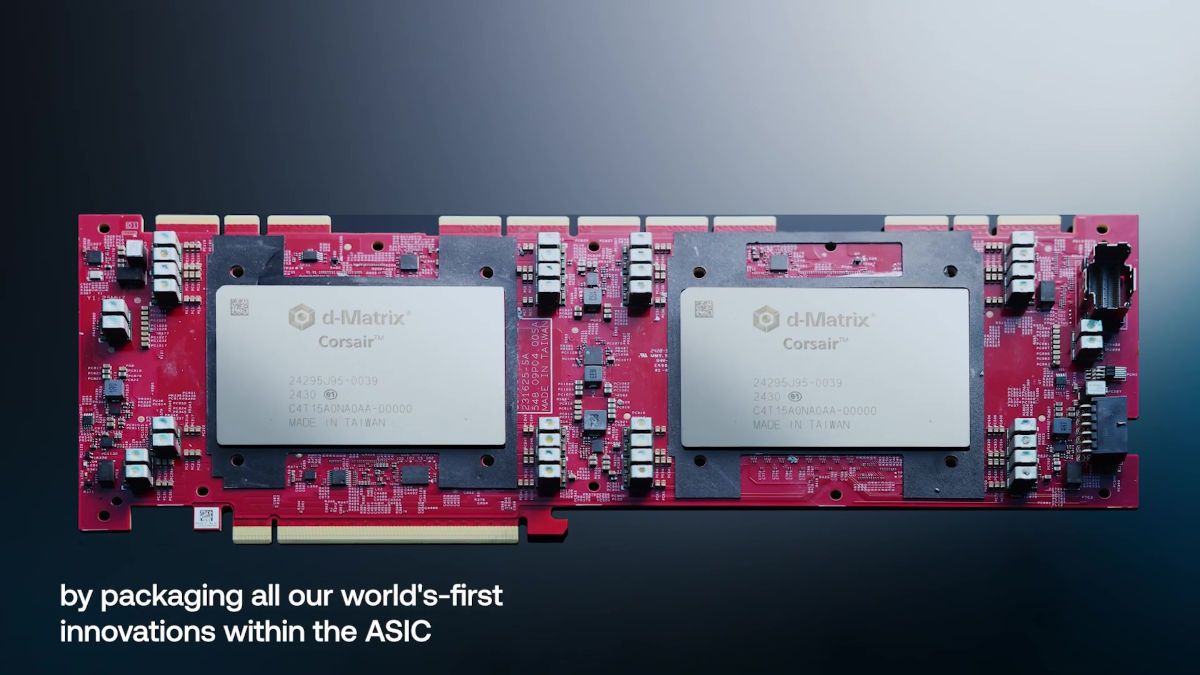

従来GPUやTPUの転用ではなく、効率を重視した推論専用の設計を導入

CEOのシド・シェスは、「学習は性能がすべてで、推論は効率がすべてです」と、Web Summit Qatarでの会話で私に語った。

この区別こそが、シェスが率いるシリコンバレー拠点の新興企業d-Matrixの根幹をなす考え方だ。今日の大規模言語モデル(LLM)の学習は、エヌビディアのハイエンドGPUやグーグルのTPU(テンソル処理ユニット)など、ごく限られた種類のチップでなければ対応できない、極めて負荷の高い作業だ。だがシェスによれば、GPUは実際にAIモデルを動かして質問に答えさせる用途には理想的ではない。にもかかわらず、業界はまさにそのGPUを使っている──主に、それしか手元にないからだ。

それは、家を建てるのに使ったハンマーと釘で、家の掃除までしているようなものだ。

「根本は、学習用のチップを使っていることです。そして『ああ、そうだ。これで推論も回そう』となる。でもそれは最善ではありません」と彼は言う。

d-Matrixは、AIのワークロードでは最終的に推論が支配的になるという信念のもとに設立された。同社は学習用ハードウェアの転用ではなく、一からアーキテクチャを構築した。シェスによれば、推論向けのチップと学習向けのチップには、アーキテクチャ上の中核的な違いがある。学習は計算(コンピュート)の問題である。だが推論は、単なる計算の問題ではないという。推論は計算とメモリー(記憶)の問題なのだ。

そして、そのメモリー部分が遅延(レイテンシー)を増やす。

LLMでは、最初の「処理」段階はしばしばプリフィル(prefill=事前充填)と呼ばれる。モデルがプロンプト(入力文)を取り込み、文脈を構築し、関連するパラメータをメモリーに読み込む段階である。その後初めて、トークン(出力の最小単位)を生成するデコード(decode)段階に入り、ユーザーが求める回答を出力し始める。この区別が重要なのは、推論の性能が生の計算力だけでなく、メモリーと処理ユニットの間でデータをいかに速く移動できるかにも制約されるからだ。計算が速くてもメモリーアクセスが遅ければ、トークン生成は滞る。メモリーが速くても計算が追いつかなければ、スループット(処理量)は落ちる。いずれにせよ、ユーザーは遅さを体感する。

「たとえば私があなたに抽象的な質問をしたとしましょう」とシェスは説明する。「すぐに答えを返すわけではないですよね。まず考える。そして2、3秒後に話し始める。その話し始める部分がデコードです」。