計算部とメモリーを近くに配置して遅延を回避

基本的に、今日のインフラの多くは、平均的な応答性よりもピーク性能を優先する学習用の処理に最適化されている。一方、推論では──特に複数の質問と回答を繰り返す対話型AIでは──レイテンシーこそが決定的な指標となる。

(余談:筆者はシェスに、アプリやブラウザーでAIが回答を書き出す速度について尋ねた。しばしば遅く感じるあの速度は、人間が受け取れるペースに合わせているのか、それとも限界いっぱいの速度なのか。端的にいえば、限界いっぱいの速度だという)

「いったん応答が始まったら、一定のペースで返してほしいものです。そうでなければ、おそらく聞いていられなくなります」と彼は付け加える。

実務的にいえば、これはモデルの重み(ウェイト=学習で調整された数値)と活性化値(アクティベーション=計算途中の中間データ)をメモリーから取り出し、トークンを生成するたびに計算ユニットへ送り込むまでの時間を最小化するということを意味する。従来のGPUアーキテクチャでは、計算部と高帯域幅メモリー(HBM)が別々のサブシステムとして分離されており、メモリー負荷の高い推論処理では非効率が生じうる。

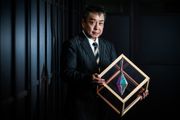

d-Matrixの解決策は、アーキテクチャ内で計算とメモリーを密接に融合させることである(d-Matrixは、DIMC[Digital In-Memory Compute]アーキテクチャと呼んでいる)。メモリーを物理的に計算部の近くに配置し、推論パターンに特化してデータの流れを最適化することで、トークンのレイテンシーを下げ、ワットあたりのトークン生成数を増やす狙いだ。さらに、単一の巨大な一枚板(モノリシック)のプロセッサを作るのではなく、シリコンをチップレット(chiplet)と呼ばれる小型のモジュール式構成要素に分割する。これらのチップレットを、処理内容の必要に応じて異なる数量で組み合わせるのである。

概念的には、従来のGPUアーキテクチャよりも、アップルのユニファイドメモリー(統合メモリー)設計に近い。計算部とメモリーの距離を縮め、ピークのベンチマーク性能ではなく効率を重視して最適化するという考え方だ。

学習用に最適化されたチップで推論を力任せにこなすのではなく、d-Matrixは推論が主流になるという前提でシリコンを設計した。その結果、特にリアルタイムの対話型処理において、低レイテンシーとワットあたりの大幅に高いFLOPS(フロップス=浮動小数点演算性能)を実現したとシェスは主張する。

そして、それがコスト上の優位性につながっている。

現時点で、d-MatrixはGPUと比べて推論処理のコストをおよそ90%低く抑えられているとシェスは述べる。しかもまだ改善の余地があるという。

「これは今日の話です」と彼は語る。「今後さらに良くなっていくだけです」。

このタイミングはまさに好機かもしれないが、やや遅きに失した感もある。OpenAIは現在、Cerebrasの巨大なプレートサイズのチップを使ってコーディング向けモデル「GPT-5.3-Codex-Spark」の推論を実行しており、他のアーキテクチャと比べて15〜20倍の高速化を達成している。Cerebrasはd-Matrixとはまったく異なるアプローチを採っているが、目指す目標は似ている。

d-Matrixは現在チップを出荷しているが、その数はまだ少なく、数百個程度にとどまる。シェスによれば、間もなく数千個規模に拡大する予定だ。早急に数百万個規模に到達する必要があるが、今年中にそこへ届く可能性もあるという。

「今年中に、量産体制を目にすることになるでしょう」と彼は筆者に語った。