7nmプロセスチップが、指の爪先ほどの大きさに200億個のトランジスタを搭載できるのに対し、5nmプロセスチップは、同じ大きさに300億個のトランジスタを搭載することが可能だ。

トランジスタの集積密度が高いほど、チップの処理速度が高速になる。IBMによると、5nmプロセスチップは、現在製品化されている10nmプロセスチップに比べて性能が40%向上し、同一性能では75%の省電力化を実現したという。

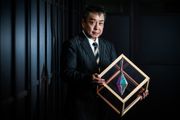

IBMは5nmプロセスチップの開発に当たって、積層したシリコンナノシートを使ったナノシートトランジスタという新しいタイプのトランジスタを採用した。現行のトランジスタ構造であるFinFETアーキテクチャのゲート数が3であるのに対し、ナノシートトランジスタは4となっている。FinFETは、22nmと14nmのチップで採用されており、7nmプロセスチップでも用いられる予定だ。

IBMリサーチで半導体グループのバイス・プレジデントを務める Mukesh Khareは「FinFETは、幾何学的スケーリングが限界に達している」と言い、半導体業界では新たなアーキテクチャへの移行が進んでいるという。チップの微細化における大きな課題は、リーク電流が増大することだ。

サムスンらも開発に参加

IBMはこれまで10年以上に渡ってナノシートトランジスタを用いたチップ技術の研究を行ってきた。同社は、ナノシートトランジスタの製造に、7nmプロセスチップと同じく半導体の微細化を実現する技術の“極端紫外線リソグラフィ”を用いたという。

IBMは、今回の研究開発をGlobalFoundriesやサムスンと共同で行い、京都で開催された回路技術の国際会議「2017 Symposium on VLSI Technology/Circuits」でその成果を発表した。IBM自身はチップの製造を行わず、GlobalFoundriesとサムスンがライセンスを受けて5nmプロセスチップを製造するオプションを持つという。また、5nmプロセスチップの量産体制は、2020年頃に整う予定だという。